## Boost MOSFETs Drive Current in Solid State AC Relay

By Kim Gauen Senior Applications Engineer, Discrete Applications Lab

Because MOSFETs are voltage controlled, they're usually very easy to drive. However, a problem arises when a power MOSFET is used as a high-side switch, such as when a load is connected to the MOSFET's source. Applications that require a high-side switch include solid-state ac or dc relays or H-bridge motor-control circuits. In these examples, it's difficult to reference the gate drive circuit and gate drive supply to the MOSFET's source.

Gate transformers, bootstrapped supplies, or optocouplers typically drive MOSFETs employed as high-side switches. For various reasons, these techniques create problems when the MOSFET must operate at high duty cycles or remain on continuously, as it might in a solid state relay. An optocoupled gate drive performs well, but it requires an isolated supply referenced to the MOSFET's source. The isolated supply drives the MOSFET's gate.

Photovoltaic diode arrays match up well when driving MOSFETs because they produce isolated output voltages of 5.0 to 10 V. But because their output current is so low ( $\approx 5.0~\mu A$ ), the MOSFET's turn-on is sluggish and noise coupled to the gate from the MOSFET's parasitic drain-to-gate capacitor can trigger undesirable switching. Buffering the array's output with a complementary emitter

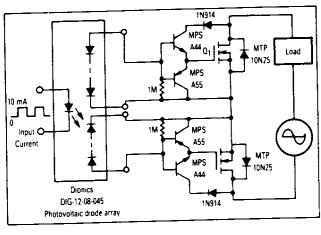

Figure 1. The emitter-follower buffer improves the MOSFET's switching speeds without an isolated gate-drive supply, an economical way to omit the floating-gate supply.

follower can improve system performance when using the photovoltaic diode array. The obvious drawback is that a floating-gate supply is still needed.

A clean and inexpensive way to eliminate the floating-gate supply is to use the voltage available at the MOSFET's drain to drive its gate (see Figure 1). Tying the collector of Q<sub>1</sub> (a high-voltage, small-signal, 400 V NPN) to the MOSFET's drain supplies sufficient gate-drive voltage when it's needed most — when the MOSFET's drain-to-source voltage is high. Two such circuits used back-to-back form an ac relay.

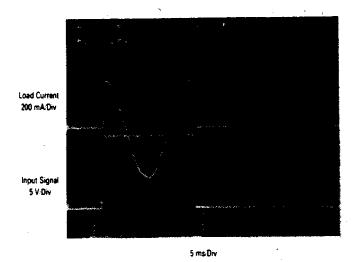

Using the emitter follower attached to the drain increases gate-drive current and decreases the MOSFET's turn-on time by a factor equal to the high-voltage NPN's beta. The resulting drain-to-source voltage fall times depend on the MOSFET's size and its required gate charge. The circuit that's used gives a fall time of 200  $\mu s$  for an MTP10N25 10 A, 250 V MOSFET. With such fall times cutting switching losses, pulse-width modulation at frequencies under 100 Hz is possible. Figure 2 shows the relay's input signal and the resulting load current.

During turn-on, VDS falls rapidly until it reaches the sum of the 1N914 diode's 0.7 V drop, the collector-emitter saturation voltage of Q1, and the gate-to-source voltage required to support the load current. At that point, the diode array completes the MOSFET's turn-on, unaided by the buffer. This slows the fall of VDS considerably when it reaches about 5.0 to 7.0 V. In high-voltage, low-frequency systems, tailing of VDS is tolerable because the tail's voltage magnitude constitutes a small fraction of the switching voltage. The 1N914 makes it possible for VGS to exceed VDS as the MOSFET completes turn-on.

The amount of current the relay can control is determined primarily by the power transistor's on-resistance. Selecting a power transistor with a low gate-to-source threshold voltage and a high transconductance will minimize the VDS waveform's tailing. Insulated-gate bipolar transistors (IGBTs) make a good choice for the power switch because they are designed to handle high current densities and they require less gate charge than a MOS-FET with a similar current rating. If an IGBT is used, a collector-emitter diode must be added. Though technically feasible, logic-level, high-voltage MOSFETs or IGBTs aren't currently available. Because they could minimize the voltage tail's magnitude and duration, they'd make a good choice for the power transistor.

Figure 2. Use of the gate drive boost technique improves switching speeds so that pulse width modulation at low frequencies is possible.